Strategic Elements and USNW to optimize RRAM technology and develop demonstrator applications

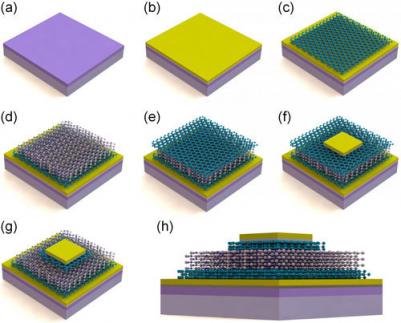

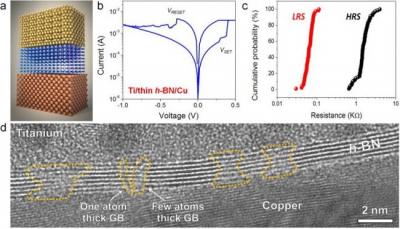

Strategic Elements announces has signed an agreement with the University of New South Wales (UNSW) to further optimize the company's Nanocube Memory Ink flexible/transparent RRAM technology. UNSW and SER will also develop demonstrator applications for the new technology.

UNSW will begin the research by assessing potential demonstrator applications in areas such as multi-functional capacitive sensors that can detect the type and strength of external stimuli including curvature, pressure, strain, and touch with clear distinction. It will also look into developing memory arrays that will fulfill the growing requirement for local digital data storage on flexible sensors, tags, wearables and high value consumer packaging.